# Il latch SR sincronizzato

In questa puntata proseguiamo lo studio del Latch SR, offrendo numerosi circuiti applicativi e analizzando le sue varianti sincronizzate.

La struttura dell'elemento di memoria SR costituisce la base da cui partire per la realizzazione di tutti gli altri tipi (che vedremo nelle prossime puntate); per questo merita ulteriori approfondimenti, cominciando con l'illustrare una serie di circuiti applicativi che, nonostante la loro struttura semplice ed economica, sono di grande utilità.

# Circuito Antirimbalzo

Uno dei principali impieghi del **Latch SR Asincrono** lo vede coinvolto nella soluzione di un fastidioso problema legato alla pressione di un pulsante o all'azione sulla levetta di un deviatore o di un interruttore; in questa situazione all'interno di questi dispositivi una barretta o una piccola lamina di metallo conduttore viene spostata (con una certa energia) da una posizione ad un'altra, posta per altro poco distante.

Per la sua natura intrinsecamente elastica questo elemento meccanico interno "vibra" in prossimità del pin d'arrivo, provocando alcuni inevitabili micro-rimbalzi che, per qualche decina di millisecondi, non gli permettono di assestarsi immobile su di esso, al fine di garantire un contatto finale stabile.

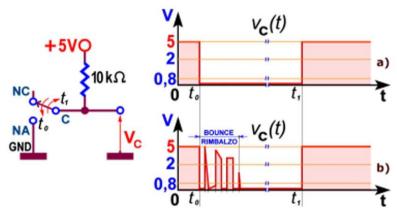

In Figura 1 si vede un deviatore con il terminale comune (Centrale, C) vincolato al positivo dell'alimentazione attraverso un resistore di Pull-Up; la condizione di uscita a 1 è ribadita anche dal fatto la levetta del deviatore sta sul terminale normalmente chiuso (NC), al quale non è collegato nulla; se (nell'istante  $t_0$ ) si sposta la levetta nella posizione opposta (sul terminale normalmente aperto, NA) la transizione sull'uscita non potrà essere quella ipotetica che suggerisce il passaggio istantaneo dell'uscita da 1 a 0 (Figura 1a); a causa del rimbalzo sul contatto d'arrivo (contact bounce) per decine di millisecondi essa subirà, invece, la presenza di alcuni impulsi attivi alti (Figura 1b), prima di assestarsi definitivamente a 0.

Se potessimo vedere il fenomeno al rallentatore si noterebbe la barretta interna toccare decisamente il pin d'arrivo, per poi lasciarlo e ritoccarlo più volte: quando essa tocca il pin "viene collegata a massa", mentre quando lo lascia "viene riportata a 1" in virtù della presenza del resistore di Pull-Up.

Nel passaggio (supposto nell'istante  $t_1$ ) dalla posizione normalmente aperta NA a quella normalmente chiusa NC accadrà certamente la stessa cosa, ma i quattro o cinque rimbalzi sul

contatto d'arrivo opposto lasceranno sempre l'uscita saldamente a 1 (senza alcun treno d'impulsi) essendo essa comunque collegata a +5V tramite il resistore.

Figura 1 - Effetto del rimbalzo sul contatto interno di un deviatore

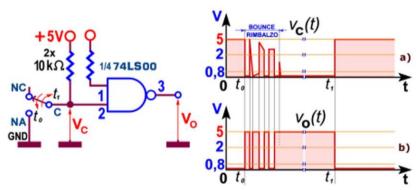

La durata e l'ampiezza dei singoli impulsi spuri è imprevedibile, ma facendoli passare attraverso una porta logica (non necessariamente "a 2 soglie" come quelli di tipo Trigger di Schmitt) possiamo squadrarli, per effetto del livello raggiunto in ingresso da ciascuno di essi, riferito ai valori tipici  $V_{IH}$  (minimo valore ritenuto 1) e  $V_{IL}$  (massimo valore ritenuto 0); la  $Figura\ 2b$  mostra questo evento dopo l'intervento di una NAND TTL a 2 ingressi (1/4 di **74LS00**): possiamo notare che l'ingresso ( $Figura\ 2a$ ) subisce la stessa dinamica descritta in precedenza, e che solo 3 dei 4 impulsi della simulazione saranno ancora presenti in uscita (ovviamente in forma invertita), poichè l'ultimo non raggiunge un'ampiezza sufficiente ( $V_{IH}$ =2V) per generarne uno sul pin 3.

Figura 2 - Effetto del rimbalzo sul contatto di un deviatore a valle di una porta logica

La necessità di comandare una logica con contatti meccanici è molto diffusa: basti pensare ai controlli di finecorsa, o ai contatti reed di un impianto di antifurto, o ai sensori di livello di un controller per liquidi; il fatto che ciascuno di essi, nell'atto della loro chiusura, "spari" sulle logiche d'ingresso una manciata di impulsi indesiderati (invece di uno solo) è intollerabile!

L'applicazione più eclatante è quella di un contatore dotato di una unità di visualizzazione (un digit con relativo decoder a 7 segmenti): se si incrementasse il suo conteggio con un pulsante, il numero sul digit sarebbe certamente inaffidabile, aumentando (in modo assolutamente imprevedibile) di due o più unità, invece di incrementarsi.

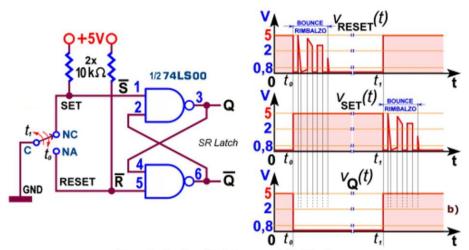

Non c'è dunque altra via se non quella di proteggere il circuito con un dispositivo antirimbalzo (**debouncer**); la soluzione classica consiste nell'utilizzo di un **Latch SR Asincrono** realizzato con 2 NOR o (come quello di *Figura 3*) con 2 NAND.

Figura 3 - Circuito antirimbalzo con un Latch SR asincrono

Vediamo in dettaglio la sequenza degli eventi possibili sul Latch, in funzione delle posizioni della levetta del deviatore chiamato a controllarlo: a) all'inizio la posizione del pin centrale del deviatore sul contatto NC collega la massa sull'ingresso S e l'uscita diretta Q è stabilmente a 1, in virtù del fatto che un resistore di Pull-Up da 10 kohm garantisce un 1 stabile anche su R (S=0, R=1); **b)** quando (nell'istante  $t_0$ ) la levetta viene spostata nell'altra posizione, istantaneamente l'ingesso S passa stabilmente a 1 (senza alcuna "strana presenza", essendo collegato a +5V tramite un resistore) mentre l'ingresso R andrà a 0 per una decina di millisecondi ma sarà subito interessato dalla successiva sequenza di alcuni impulsi attivi alti, dovuti al noto rimbalzo della lamina interna sul contatto d'arrivo; c) in queste condizioni, non appena si tocca il contatto NA e la massa del centrale passa sull'ingresso R, l'uscita scatta a 0 in pochi nanosecondi (in un tempo pari a quello di propagazione della porta NAND) e starà stabilmente in questo stato, ignorando del tutto la presenza del treno di impulsi spuri: nonostante R passi più volte da 0 a 1 la tabella di verità del Latch SR assicura la memorizzazione dello stato precedente se, dopo averlo assunto, i suoi ingressi sono entrambi a disattivi (S=1, R=1), e questa è proprio la situazione che si manifesta quando il contatto del deviatore stacca brevemente la massa da R per effetto del rimbalzo su NA; d) dopo alcune decine di millisecondi anche l'ingresso R si assesterà definitivamente a 0, ma la sua storia precedente, travagliata da picchi di tensione indesiderati, non avrà avuto alcuna influenza sull'uscita; e) quando (nell'istante t<sub>1</sub>) si vorrà tornare dalla posizione NA a quella NC, su S e R accadrà certamente la stessa cosa, a ruoli invertiti, ma i 4 o 5 rimbalzi sul contatto d'arrivo opposto lasceranno comunque l'uscita diretta Q saldamente a 1, senza alcuna interferenza.

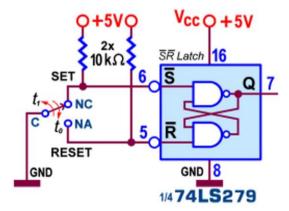

Figura 4 - Circuito antirimbalzo con Quad S-R Latches 74LS279

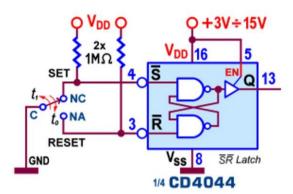

Figura 5 - Circuito antirimbalzo con Quad NAND S-R Latches 4044

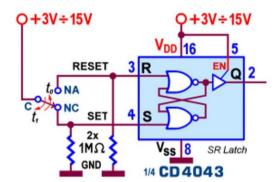

Figura 6 - Circuito antirimbalzo con Quad NOR S-R Latches 4043

In conclusione non possiamo non rendere grazie a questo piccolo circuito che, con sole 2 porte logiche risolve un grosso problema; lo schema di *Figura 3* può naturalmente essere realizzato anche con elementi degli integrati specifici, per esempio sostituendo le 2 NAND **74LS00** con 1/4 di **74LS279** (*Figura 4*); in virtù delle loro alte impedenze d'ingresso, con i componenti CMOS **4043** (Quad NOR S-R Latches, *Figura 5*) o **4044** (Quad NAND S-R Latches, *Figura 6*) i resistori (rispettivamente di Pull-Up e di Pull-Down) potranno essere scelti di valore anche decisamente più grande.

In ogni caso vale a pena ricordare che il fenomeno del rimbalzo (tipicamente di 10 o 20 ms) non dura in genere più di 50 ms, un tempo mille volte più grande rispetto a quello di commutazione delle porte logiche.

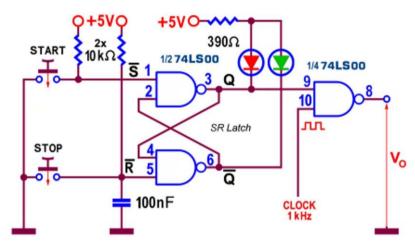

#### **Controllo Start-Stop**

La natura bistabile del **Latch SR Asincrono** si presta egregiamente anche per il controllo dei segnali chiamati a dar vita a molti dispositivi digitali; più correttamente, la presenza di un **SR** può intervenire sulle porte logiche che ne controllano il passaggio, dando luogo al cosiddetto **gating** di clock, già analizzato un una passata occasione.

Il circuito di *Figura 7* utilizza 2 pulsanti normalmente aperti per far partire (Start) e/o bloccare (Stop) il conteggio di un Cronometro o, in generale, di un contatore: l'effetto è più godibile se si dispone di una unità di visualizzazione; non serve perdere molto tempo per capire che una breve azione sul pulsante Start (con quello di Reset aperto, cioè a riposo) impone la condizione (S=0, R=1) per cui l'uscita diretta Q passa 1, aprendo la porta che controlla il clock di 1 kHz e autorizzando l'avanzamento continuo del conteggio, fino all'intervento della condizione opposta (S=1, R=0), dovuta alla pressione sul pulsante Stop, che ovviamente riporterà Q a 0, chiudendo la porta di gating.

Certamente ci si può chiedere perchè non usare direttamente, in ingresso al contatore, un semplice deviatore (o un interruttore) meccanico; fermo restando che l'investimento economico non è molto distante da quello dell'acquisto di un 74LS00, sappiamo già che la cosa (pur praticamente più semplice) non è ammissibile, per la presenza dei rimbalzi generati nel momento della commutazione, che massacrerebbero il segnale di clock introducendo alcuni impulsi spuri che non devono essere presenti.

Per eccesso di zelo il circuito comprende anche la disponibilità di un *reset automatico* e di una coppia di led (o di un led bicolore) che esprimono lo stato della *porta di gating*, aperta (led verde acceso per la presenza di un livello 0 sull'uscita negata, Q=0) o chiusa (led rosso acceso, essendo a 0 l'uscita diretta, Q=0).

Figura 7 - Controllo di un segnale ad onda quadra: Circuito

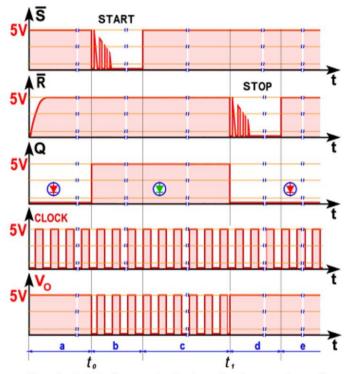

Il diagramma temporale (Figura 8), sempre consigliabile nell'analisi dei circuiti sequenziali, mette in evidenza ogni dettaglio: a) all'accensione la presenza di un resistore di Pull-Up da 10 kohm garantisce un 1 stabile su S mentre la differenza di potenziale nulla ai capi del condensatore tiene a 0 l'ingresso R per un tempo proporzionale alla costante  $T=RC=10^4*100*10^{-9}=1$  ms; questa situazione (S=1, R=0) forza istantaneamente a 0 l'uscita diretta Q, che manterrà questo stato fino a nuovo evento anche dopo che, rapidamente, la carica del condensatore avrà portato a 1 anche l'ingresso R (S=1, R=1); in queste condizioni la porta è chiusa e il segnale di clock non passa sul contatore; b) premendo il pulsante Start (nell'istante t<sub>0</sub>) il corrispondente ingresso S viene forzato a 0 per una decina di millisecondi (S=0, R=1), ma sarà subito interessato da una successiva sequenza di impulsi attivi alti, dovuti al rimbalzo sul contatto della lamina interna; nell'istante to l'uscita scatta a 1 in pochi nanosecondi (cioè in un tempo pari a quello di propagazione della porta NAND) e (come assicura la tabella di verità del Latch SR) rimarrà stabilmente in questo stato, ignorando del tutto la presenza del treno di impulsi indesiderati, nonostante S passi più volte da 0 a 1; ora la porta è aperta e lascia passare il segnale di clock; c) l'intervallo indicato dalla lettera b ha una durata di non meno di 200 ms, tipicamente associati al tempo (di reazione umano) necessario per dare una brevissima pressione sul tasto; la porta rimarrà aperta anche per tutto l'intervallo di tempo c, grande a piacere in funzione delle necessità di disporre del clock sul dispositivo a valle; d) quando il momento è arrivato (istante  $t_1$ ) si potrà intervenire sul pulsante Stop, innescando una situazione identica a quella descritta per il tasto Start: il corrispondente ingresso R passa a 0 per pochi millisecondi (S=1, R=0) e l'uscita diretta scatta istantaneamente a 0, rimanendo stabilmente in questo stato, nonostante la presenza del treno di impulsi attivi alti generati successivamente dal rimbalzo sul contatto interno; il tempo necessario per una breve pressione è sempre di almeno 200 ms, dopodiché anche l'ingresso R tornerà a 1; di sicuro, a partire dall'istante t<sub>1</sub>, la porta verrà chiusa, inibendo il passaggio del clock fino a nuovo evento.

Figura 8 - Controllo di un segnale ad onda quadra: diagramma temporale

Per correttezza, nel diagramma temporale va tenuto presente che, per praticità didattica, l'andamento degli impulsi di rimbalzo è mostrato in un intervallo di tempo di gran lunga inferiore a quello ad essi relativo (qualche decina di ms), cosa evidente confrontandolo con quello utilizzato sia per il periodo T del segnale di clock che per la costante di tempo T, entrambe di 1ms.

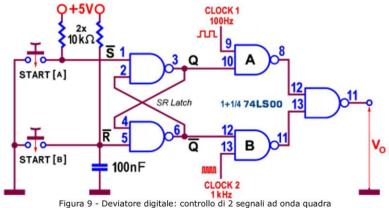

## **Deviatore digitale**

Una variante del circuito appena descritto (vedi Figura 9) si occupa di governare la velocità di un dispositivo digitale offrendo l'opportunità di scegliere tra 2 forme d'onda quadra di diversa frequenza; la filosofia è ancora quella descritta in precedenza: solo uno dei 2 clock passerà in ingresso al dispositivo da controllare, in virtù del fatto che le due uscite del Latch SR Asincrono sono sempre alternative tra loro.

La struttura d'uscita è la classica AND-OR realizzata con 3 porte NAND e, visto che non si può fare a meno di 2 integrati 74LS00, può eventualmente essere sostituita con 1/4 di multiplexer 74LS157 (Quadruple 2-Line to 1-Line MUX); nel progetto è mantenuta la presenza del condensatore da 100 nF, il cui compito è ora quello di garantire in uscita, all'accensione, il segnale più veloce.

#### **Nuovi Latches SR Asincroni**

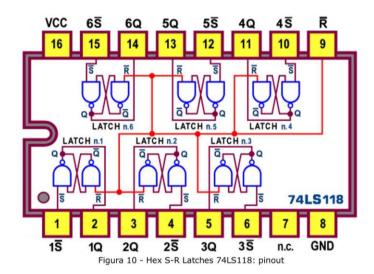

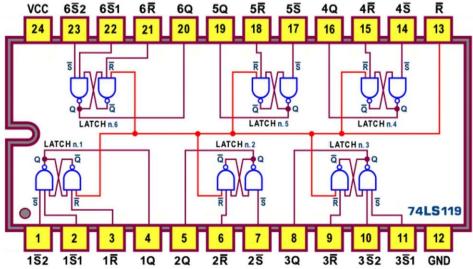

Prima di affrontare l'evoluzione Sincrona dei Latches SR voglio proporre due assolute rarità, per altro (con qualche difficoltà) ancora reperibili, a complemento di quelle illustrate la scorsa puntata; si tratta di 2 componenti TTL, definiti dai costruttori Hex S-R Latches, contenenti entrambi 6 Latches SR in logica negativa (cioè realizzati con NAND e soggetti a ingressi attivi bassi): quelli del 74LS118 (pinout in Figura 10) sono caratterizzati dal fatto di disporre di 6 linee di Set indipendenti e una sola linea di Reset in comune; nel 74LS119 (pinout in Figura 11) c'è ancora una linea di Reset in comune, affiancata ora da un'altra, indipendente, per ciascun Latch; la metà di essi dispone inoltre di 2 linee di Set invece di una sola.

Figura 11 - Hex S-R Latches 74LS119: pinout

## **Latch SR Sincrono**

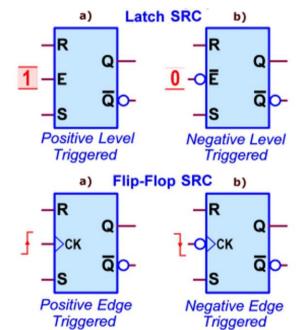

La letteratura digitale propone a questo punto la possibilità di disporre di una linea di controllo aggiuntiva, al fine di autorizzare i cambiamenti delle uscite del Latch SR solo in ben precisi intervalli di tempo; non di rado a questa linea è attribuito il nome di Clock C, inducendo anche per il dispositivo la definizione impropria di Flip-Flop SRC, ma noi sappiamo che questo attributo spetta solo alle memorie che cambiano stato su uno dei fronti attivi del segnale di sincronismo.

Poiché il dispositivo è invece attivo sui livelli della linea di controllo, è certamente più corretto riferirsi al primo come a un Latch SR Sincrono o Gated Latch e chiamare la seconda con il nome di Abilitazione E, Enable.

Figura 12 - Latch SRC Sincrono: circuito e Tabella delle Transizioni

La Figura 12 mostra una sua realizzazione con porte NAND (un solo integrato 74LS00); nonostante l'apparenza si tratta di un Latch SR che lavora in logica positiva: se E=0 entrambi gli ingressi interni S' e R' sono a 1 e il Latch è bloccato in condizione d'attesa (cioè memorizza lo stato assunto in precedenza); se E=1 le porte di controllo sono aperte, lasciando passare dei segnali di livello opposto di quelli applicati (si dice che il Latch è "trasparente"), imponendo alle uscite gli stati previsti dalla Tabella delle Transizioni, riportata in figura insieme all'equazione caratteristica dell'elemento di memoria.

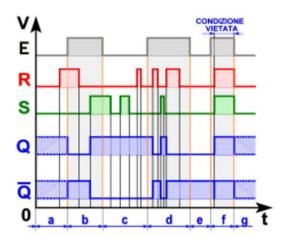

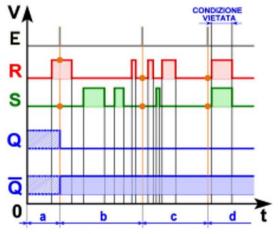

Il Diagramma Temporale di Figura 13 ribadisce il concetto; in dettaglio: a) all'accensione il valore logico delle uscite è imprevedibile (se non si prendono provvedimenti per imporre uno dei 2 stati, con le tecniche descritte in precedenza) e permane tale anche se gli ingressi hanno, nel frattempo, assunto livelli stabili, fin tanto che l'Abilitazione E rimane a 0; b) non appena E passa a 1 (fronte di salita di E) le uscite inseguono gli ingressi: con S=0, R=1 viene imposta la condizione S'=1, R'=0 e l'uscita diretta del Latch passa a 0; con S=1, R=0 viene forzata la condizione opposta, S'=0, R'=1 che mette a 1 l'uscita diretta; con entrambi gli ingressi a 0 (S'=1, R'=1) l'uscita del Latch non subisce variazioni; c) quando E torna a 0 (fronte di discesa di E) il Latch non è più sensibile alle variazioni dei segnali S e R e mantiene lo stato rilevato in questo istante, per tutto il tempo in cui rimane a 0.

Naturalmente anche con questa variante sincrona bisogna guardarsi dal fornire la combinazione vietata (S=1, R=1 e quindi S'=0, R'=0), almeno quando il *Latch* è abilitato (E=1); questa situazione (visibile nel dettaglio **f** di *Figura 13*) forzerebbe a 1 entrambe le uscite: non solo la cosa è logicamente inaccettabile (essendo in contrasto con l'ipotesi che esse debbano sempre essere complementari l'una dall'altra) ma (se si suppone di riportare gli ingressi a 0 nel medesimo istante) il Latch si porta in uno stato metastabile dal quale per altro esce quasi subito, attestando però le sue uscite a valori imprevedibili, imposti dalla NAND che per prima "sentirà" lo 0 in ingresso, per l'inevitabile differenza tra i rispettivi tempi di propagazione.

Figura 13 - Latch SRC Sincrono: Diagramma Temporale 1

La disponibilità dell'Abilitazione rende dunque più affidabile il **Latch SRC**, consentendo l'aggiornamento del suo stato quando (per esempio) si è ben certi che gli ingressi S e R sono stabili; come detto, è certamente attivo sui livelli (**Level Triggered**) della linea E, ma nulla vieta di pensare ad essa come ad un segnale basso con dei brevissimi impulsi a 1, un treno d'impulsi (segnale "a pettine", *comb signal*) ciascuno dei quali è sostanzialmente racchiuso dai suoi 2 fronti di salita e di discesa, così da essere ritenuti pressocché coincidenti.

In queste condizioni il dispositivo sembra si possa ritenere attivo su fronti (*Edge Triggered*) e confuso con un *Flip-Flop* (da qui, probabilmente, il refuso sulla sua effettiva natura): in realtà per poter appartenere a questa categoria il dispositivo deve essere dotato internamente anche di un circuito speciale, detto *Rivelatore di Transizione*, come vedremo più avanti; la *Figura 14* mostra come cambia il Diagramma Temporale, dando luogo a uscite completamente diverse (tra l'altro, nell'esempio, anche la sciagurata condizione vietata viene ignorata).

Figura 14 - Latch SRC Sincrono: Diagramma Temporale 2

# Flip-Flop SR Master-Slave

Rendere breve il segnale di Abilitazione può evitare cambiamenti di stato indesiderati, dovuti ad instabilità dei segnali di ingresso, consentendo una sola commutazione delle uscite

(riducendo ad un istante l'effetto "trasparenza" del *Latch*) invece della probabile sequenza, autorizzata da un livello E lasciato alto per un tempo di una certa consistenza; ma esso non può nemmeno essere troppo breve, perché deve durare almeno tanto da consentire alla memoria di commutare.

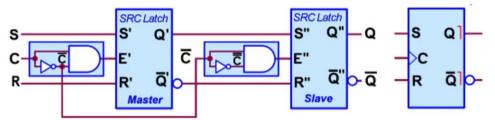

Per conciliare entrambe le esigenze è stato studiato un dispositivo formato da 2 distinti *Latches SR Sincroni*, indipendenti l'uno dall'altro, posti in cascata tra loro, ma abilitati in tempi diversi; esso è noto come *Flip-Flop Master-Slave* (o *Pulse-Triggered*, vedi *Figura 15*), ma in realtà si tratta ancora di un *Latch*, sebbene le sue uscite Q sembrino effettivamente cambiare sul fronte (di discesa) dell'Abilitazione (ancora una volta detta *Clock*, in modo improprio).

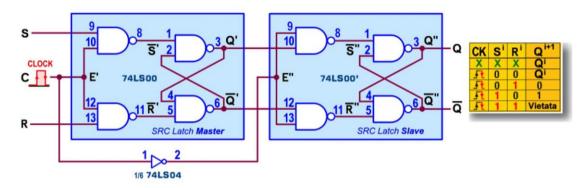

Figura 15 - Flip-Flop Master-Slave (Pulse Triggered): circuito e Tabella delle Transizioni

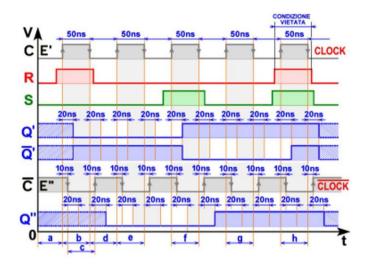

L'artificio che rende importante questo dispositivo sta nel presentare il segnale di Abilitazione in forma diretta al primo Latch SR Sincrono (detto Master) e in forma negata al secondo (detto Slave); vediamo un'analisi dettagliata, supportata dal relativo Diagramma Temporale di Figura 16: a) all'accensione il valore logico delle uscite di entrambi i Latches è (al solito) imprevedibile; fin che il Clock C rimane a 0 non succede nulla, anche se gli ingressi esterni hanno assunto livelli stabili: le porte del Master sono chiuse, impedendo qualunque aggiornamento dall'esterno, e quelle dello Slave sono aperte, mantenendo stabili i valori in uscita, per altro non ancora definibili; b) non appena C passa a 1 (cioè sul fronte di salita di C) le porte di Abilitazione E' del Master lasciano passare gli ingressi esterni e le sue uscite Q' si assestano al valore suggerito dalla Tabella di Verità: nell'esempio S=0 e R=1 per cui l'uscita diretta interna Q' passa a 0; c) quasi contemporaneamente la condizione C=1 viene invertita e proposta sulle porte di Abilitazione dello Slave (E"=0), chiudendo le sue porte e impedendo il passaggio all'informazione preparata dal Master; lo stato delle sue uscite Q", ancora indefinite, non potrà essere variato; d) quando lo si ritiene opportuno (di solito dopo qualche decina di ns) il clock viene riportato a 0 togliendo (sul suo fronte di discesa) l'Abilitazione alle porte del Master (E'=0) e fornendola poco dopo (E"=1) alle porte dello Slave, le uscite del quale, Q", si assesteranno dunque al valore suggerito dallo stato assunto in precedenza dalle uscite Q' del Master.

In concreto la forma d'onda di clock produce effetto in ogni sua parte: 1) sul fronte di salita (e per tutto il tempo in cui rimane a 1) consente al Master di funzionare e blocca lo Slave: in questo modo le uscite Q'' dello Slave rimangono stabili al valore precedentemente memorizzato, a beneficio dei circuiti a valle, senza essere influenzate dalle variazioni degli ingressi esterni, inseguiti invece dalle uscite Q' del Master senza influenzare quelli dello Slave; 2) sul fronte di discesa (e per tutto il tempo in cui C rimane a 0) succede l'opposto: il Master viene bloccato e il valori stabili delle proprie uscite Q' influenzeranno quelle Q'' dello Slave (ora abilitato), aggiornando le informazioni a valle in modo del tutto indifferente alle variazioni sugli ingressi esterni.

Figura 16 - Flip-Flop Master-Slave (Pulse Triggered): Diagramma Temporale

Nel Diagramma Temporale la situazione **e)** e **g)** si riferisce al caso S=0 e R=0 per cui l'uscita diretta interna Q' del Master rimane inalterata al valore precedente; nella situazione **f)** il Master forzerà la sua uscita diretta interna Q' a 1, essendo S=1 e R=0; la situazione **h)** simula infine la condizione vietata, S=1 R=1, assolutamente da non fornire mai!: sappiamo infatti che in queste condizioni le uscite Q' del Master scattano entrambe a 1 e nel momento in cui gli ingressi sono tolti (sul fronte di discesa del Clock) le uscite stesse si assestano, dopo un breve periodo di incertezza, ad un valore imprevedibile.

Naturalmente, in tutti i casi precedenti, le uscite Q'' dello Slave subiranno la stessa sorte, qualche istante dopo.

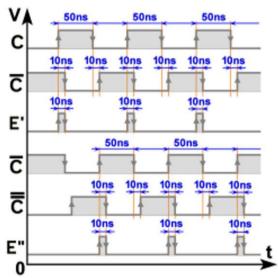

Nel Diagramma Temporale abbiamo utilizzato un segnale di clock C di 50 ns, fornito istantaneamente (E') alle porte del Master e poco dopo (E'') a quelle dello Slave, ritenendo verosimile un ritardo di propagazione di 10 ns dovuto all'inverter **74LS04**; in entrambi i casi abbiamo supposto che le rispettive uscite (Q' del Master e Q'' dello Slave) subiscano un ritardo di 20 ns, per tener conto del tempo necessario ai segnali coinvolti per attraversare le porte **74LS00**, prima di raggiungerle.

Figura 17 - Flip-Flop Master-Slave (Pulse Triggered): schema funzionale e simboli logici

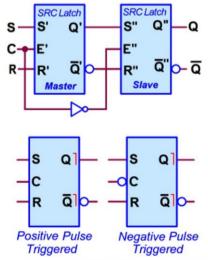

La *Figura 17* mostra lo schema logico e il simbolo che rappresenta il *Flip-Flop Master-Slave* (*Pulse-Triggered*); in quest'ultimo, il fatto che le sue uscite Q commutano effettivamente alla fine (sul fronte di discesa) dell'impulso di Clock è messo in evidenza con una particolare segno "ad angolo retto", detto *postponed output indicator*.

#### Flip-Flop SR Master-Slave Data Lock-Out

Il circuito didattico di *Figura 15* è noto per la sua capacità di risolvere il suo compito con affidabilità, memorizzando il dato in uscita (se gli ingressi sono mantenuti stabili) solo sul fronte di discesa dell'Abilitazione, e mantenendo la memoria di questo evento in tutte le altre parti della sua forma d'onda; tuttavia esiste un fatto interessante e ineludibile: l'inverter **74LS04** non può operare senza ritardo, per cui è facile verificare che, per un breve periodo (10 ns) dopo il fronte di salita del clock, entrambi i sincronismi di memorizzazione E' e E'' sono attivi contemporaneamente, cosicché entrambe le coppie di porte di controllo rimangono aperte!

Oggettivamente questo fatto potrebbe produrre comportamenti indesiderati e imprevedibili, ma la possibilità che questi si manifestino è molto poco probabile; per di più nella progettazione dei componenti commerciali di questo tipo vengono utilizzate tecniche particolari, rivolte a rendere "disgiunti" (cioè effettivamente separati e non sovrapposti) i due segnali di sincronismo E' e E".

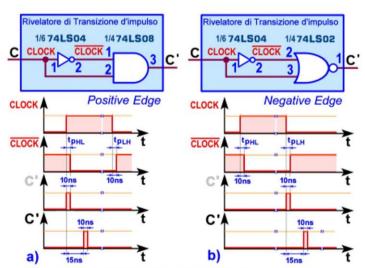

In sostanza la forma d'onda di clock viene sottoposta ad un **Rivelatore di Transizione** (Figura 18), funzionalmente non dissimile da un multivibratore monostabile; la durata del brevissimo impulso, da esso generato direttamente dentro il Flip-Flop, è pari a quella del ritardo di propagazione dell'inverter **74LS04**, tipicamente pari a **10 ns** per entrambe le transizioni, **t**<sub>PLH</sub> e **t**<sub>PHL</sub>; in questo modo la successiva porta logica riesce sostanzialmente a "rivelare" (cioè a mettere in evidenza, isolandolo) solo il fronte di salita (se si tratta di una AND **74LS08**) oppure solo il fronte di discesa (se si tratta di una NOR **74LS02**) della forma d'onda di clock fornita su C.

Va messo in evidenza che l'effettivo impulso di sincronismo C' sarà disponibile per il *Latch* solo dopo un ulteriore ritardo, tipicamente di **15 ns**, dovuto al tempo di propagazione della porta logica; inoltre i fronti dei segnali coinvolti sono disegnati "verticali", ipotizzando nulli i rispettivi *tempi di transizione* (quelli consumati per passare dal 10% al 90% del valore di tensione a livello alto).

Figura 18 - Circuito Rivelatore di fronte e Diagramma Temporale

La *Figura 19* mostra la versione di *Flip-Flop Master-Slave* dotata di 2 di questi dispositivi di rivelazione del fronte, detto *Data Lock-Out*, per sottolineare che le porte di entrambi i *Latches SR* lasceranno passare i dati presenti sui rispettivi ingressi agganciandoli (bloccandoli, *Lock-Out*) solo per un breve istante, a partire dal fronte di salita rispettivamente di C e di C negato, evitando ogni possibile effetto collaterale.

Figura 19 - Flip-Flop Master-Slave Data Lock-Out: circuito e simbolo logico

La presenza del triangolino all'interno del simbolo logico sull'ingresso C ci autorizza a ritenere questo elemento di memoria un Flip-Flop a tutti gli effetti.

La Figura 20 illustra in dettaglio i 2 segnali di sincronismo E' e E", evidenziando quanto finora sostenuto: Master e Slave risultano ora "trasparenti" per un tempo piccolissimo, in 2 posizioni ben distinte tra loro, rendendo inutile mantenere costanti gli ingressi esterni mentre C=1.

Figura 20 - Flip-Flop Master-Slave Data Lock-Out: Diagramma Temporale delle Abilitazioni

# Flip-Flop SR

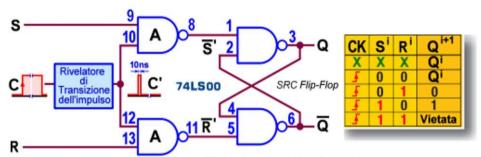

La tecnica appena descritta per trasformare il **Master-Slave** in vero Flip-Flop (cioè sensibile ai fronti del clock) è riutilizzabile anche per trasformare un **Latch SRC** in un **Flip-Flop SR** (detto anche **Edge Triggered SR**): dopotutto esso corrisponde alla metà di un **Data Lock-Out**. Certa letteratura offre altri modelli, più sofisticati, ma noi possiamo riferirci alla classica versione didattica di *Figura 21*: sebbene non esistano componenti commerciali di **Flip-Flop SR** essa è importante perché costituisce la base di sviluppo di tutti gli altri tipi di **Flip-Flop**, oggetto delle nostre successive analisi.

Già sappiamo che il circuito Rivelatore di Transizione trasforma il segnale di Abilitazione in un breve impulso attivo alto, in corrispondenza di uno dei suoi fronti; utilizzando quello di Figura 18a avremo si disporrà di un **Positive Edge Triggered SR**, mentre con quello di Figura 18b si parlerà di Negative Edge Triggered SR.

Figura 21 - Flip-Flop SR: circuito e Tabella delle Transizioni

Di certo abbiamo ora a che fare con un Flip-Flop SR, non più con un Latch; la Figura 22 mostra i simboli logici delle 2 categorie, supposte entrambe con ingressi attivi alti: il primo è sempre interessato da un Clock C e il fatto di essere attivo sui suoi fronti è indicato dalla presenza di un triangolino all'interno del simbolo; il secondo è sempre interessato da un Enable E (cioè attivo sui suoi livelli, anche se talvolta chiamato impropriamente clock) ed è sempre rappresentato senza il citato triangolino.

Figura 22 - Latch SRC Sincrono e Flip-flop SR (Edge Triggered): simboli logici