${\it Il\ Latch\ D}$  (prima parte)

Prosegue in questa puntata lo studio dei Latches e dei Flip-Flop presenti sul mercato; affronteremo quelli di tipo D-Latch, un importante elemento di memoria dal comportamento "trasparente" nei confronti dei dati elaborati, molto utile nei progetti sequenziali.

Continuiamo l'analisi degli elementi di memoria, piccole macchine sequenziali che influenzano le loro uscite non solo in funzione dei valori presenti sui loro ingressi esterni ma anche dello stato da essi assunto in un tempo precedente; tra le numerose varianti cominceremo con i dispositivi **D-Latch**, riservandoci di completarne la ricca trattazione in una successiva puntata.

## **Latch D (memorie D-Latch)**

L'elemento di memoria Tipo D è la naturale evoluzione di un **Latch SR**: l'idea di utilizzare un unico ingresso D, collegato direttamente ad R e tramite un inverter a S, risolve drasticamente il problema della "condizione vietata" di quest'ultimo: poiché essa si manifesta quando entrambi gli ingressi S e R sono attivi (bassi) è facile verificare che ora non potrà mai realizzarsi.

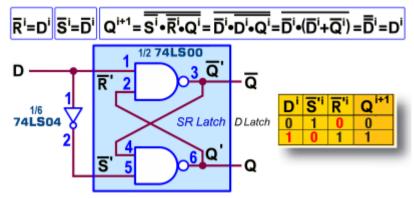

Figura 1 - Latch D Asincrono: circuito e Tabella delle Transizioni

La *Figura 1* mostra la versione *Asincrona* di un *Latch D*, insieme alla sua formula caratteristica, Q<sup>i+1</sup>=D<sup>i</sup>, per arrivare alla quale (ultimo passaggio) si è fatto riferimento al "teorema dell'assorbimento" dell'Algebra di Boole, A\*(A+B)=A, duale di A+AB=A; appare evidente che l'uscita diretta Q *inseguirà* l'ingresso esterno D, riproponendone continuamente il valore corrente dopo un breve istante, dovuto ai tempi di propagazione delle porte logiche

utilizzate; questo fatto giustifica la ragione del nome **D** affidato a questo dispositivo, per sottolineare che l'informazione fornita in ingresso sarà disponibile direttamente in uscita dopo un certo ritardo (Delay).

Di fatto questo elemento di memoria è però utilizzabile solo con una determinata linea di controllo aggiuntiva, al fine di autorizzare i cambiamenti delle uscite solo in ben precisi intervalli di tempo; sebbene a guesta linea sia spesso attribuito il nome di Clock C (autorizzando per questo dispositivo la definizione impropria di Flip-Flop D-Latch) abbiamo già sottolineato (nella puntata scorsa) che questo attributo spetta solo alle memorie che cambiano stato su uno dei fronti attivi del segnale di sincronismo. Per questa ragione (essendo il dispositivo attivo sui livelli della linea di controllo) è certamente più corretto chiamarla Abilitazione **E**, *Enable*.

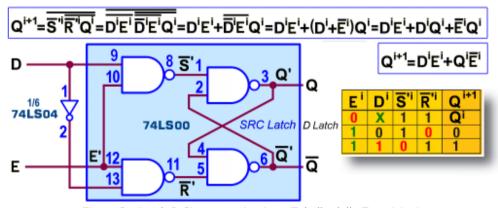

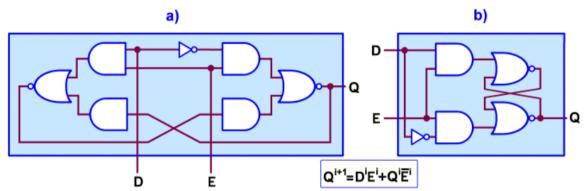

La Figura 2 mostra il circuito di un **D-Latch** ricavato da un **Latch SR Sincrono**: se E=0, per qualunque valore di D, gli ingressi interni S' e R' sono entrambi a 1 e il Latch è bloccato in condizione d'attesa (cioè memorizza lo stato assunto in precedenza); se E=1 le porte di controllo sono aperte, lasciando passare segnali di livello opposto (per la presenza dell'inverter) rispetto a quelli applicati: anche in questa variante l'uscita diretta Q inseguirà il valore corrente dell'ingresso esterno D e il dispositivo si comporterà in modo "trasparente", fino a quando la linea di controllo non verrà di nuovo disabilitata (E=0).

La presenza della linea E rende un po' più complessa la formula caratteristica (vedi Figura 2) per arrivare alla quale (ultimo passaggio) si è fatto riferimento al "teorema del consenso" dell'Algebra di Boole, AB+BC+AnegatoC=AB+AnegatoC, ma al tempo stesso la sintetizza immediatamente, non appena le si fa assumere uno dei suoi due valori: Qi+1=Di (come prima, con E=1) e  $Q^{i+1}=Q^{i}$  (con E=0).

Figura 2 - Latch D Sincrono: circuito e Tabella delle Transizioni

Questo fatto mette in evidenza un altra fondamentale utilità di questo dispositivo: esso realizza una memoria statica ad un bit, il prototipo di quella ampiamente utilizzata e indispensabile nei progetti basati su componenti programmabili; per questa ragione la lettera D che lo identifica può essere associata anche alla parola Data.

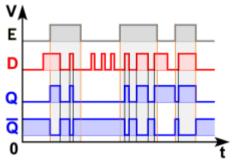

La disponibilità dell'abilitazione E rende il **D-Latch** attivo sui livelli (**Level Triggered**) di questa linea, imponendo alle sue uscite il valore dell'ingresso D per tutto il tempo in cui E=1 e memorizzando quello presente nell'istante corrispondente al fronte di discesa di E; il Diagramma Temporale di Figura 3 ribadisce il concetto; in dettaglio: a) all'accensione il valore logico delle uscite è imprevedibile ma, in questo esempio, si è supposto che l'uscita diretta Q sia stata forzata a 0 da un circuito di Reset automatico; poichè il sincronismo d'Abilitazione E è ancora disattivo essa mantiene valore nullo anche in presenza di eventuali variazioni sull'ingresso D; b) non appena E passa a 1 (fronte di salita di E) le uscite inseguono l'ingresso D: con D=0 viene imposta la condizione S'=1, R'=0 e l'uscita diretta del Latch passa a 0; con D=1 viene forzata la condizione opposta, S'=0, R'=1 che mette a 1 l'uscita diretta; c) quando E torna a 0 (fronte di discesa di E) il Latch aggancia il valore corrente assunto in quel momento da D, copiandolo in uscita e mantenendolo per tutto il tempo in cui rimane a 0.

Figura 3 - Latch D Sincrono: Diagramma Temporale

In occasione della descrizione dei decoder a 7 segmenti con memoria (i sofisticati BCD to 7segment Latch/Decoder/Driver 4511 e 9368) abbiamo anticipato la descrizione di questo tipo di memoria, suggerendone l'impiego come generatore dell'effetto intertempo, nel progetto di un cronometro digitale: a) rendendo trasparente la memoria del decoder (proprio di tipo D-Latch) l'informazione da esso prodotta (a partire dal codice BCD generato da un contatore a monte) viene passata sul suo digit, consentendo la visualizzazione del tempo corrente; b) intervenendo sulla linea di controllo (per esempio con il segnale di una fotocellula posta in un dato punto del percorso sportivo) è possibile congelare il tempo corrente per qualche istante, per mostrare appunto un tempo intermedio.

Tuttavia l'effetto "trasparenza" utilizzato in questi termini non sempre è producente; se bisogna assicurare agli utilizzatori a valle l'informazione presente a monte in un determinato momento è necessario evitare cambiamenti di stato indesiderati, dovuti ad instabilità dei segnali di ingresso, consentendo una sola commutazione delle uscite; per ottenere questo risultato bisogna esser ben certi che l'ingresso D sia stabile e, al tempo stesso, pensare al segnale di abilitazione E come ad un brevissimo impulso a 1 (sostanzialmente racchiuso dai suoi 2 fronti di salita e di discesa, così da essere ritenuti pressocché coincidenti), breve ma non troppo, per dare alla memoria almeno il tempo per commutare.

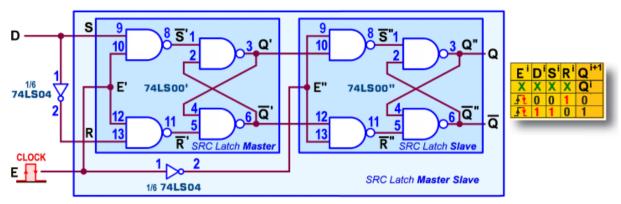

Una soluzione adatta a conciliare entrambe le esigenze è quella di utilizzare un **D-Latch** Master-Slave, adattando con un inverter gli ingressi S e R di un Latch SR Master-Slave (analizzato la scorsa puntata in ogni dettaglio); la Figura 4 mostra il suo schema e la sua Tabella delle Transizioni.

Questo dispositivo utilizza ogni parte della forma d'onda d'Abilitazione (detta impropriamente clock) e per questo appartiene alla categoria dei Pulse-Triggered; ricordiamone brevemente il suo principio di funzionamento: a) sul fronte di salita (e per tutto il tempo in cui E rimane a 1) abilita il funzionamento del Master e blocca quello dello Slave: in questo modo le uscite Q'' di quest'ultimo rimangono stabili al valore precedentemente memorizzato, a beneficio dei circuiti a valle, senza essere influenzate dalle variazioni dell'ingresso esterno D, inseguito invece dalle uscite Q' del Master senza influenzare lo Slave; b) sul fronte di discesa (e per tutto il tempo in cui E rimane a 0) succede l'opposto: il Master viene bloccato e il valori stabili delle proprie uscite Q' influenzeranno quelle Q' dello Slave (ora abilitato), aggiornando le informazioni a valle in modo del tutto indifferente alle variazioni sull'ingresso esterno D.

Figura 4 - Latch D Master-Slave (Pulse Triggered): circuito e Tabella delle Transizioni

In conclusione il **D-Latch Master-Slave** memorizza il dato presente in ingresso (se mantenuto stabile) solo sul fronte di discesa dell'Abilitazione, mantenendo in uscita la memoria di questo evento durante tutte le altre parti della sua forma d'onda; tuttavia vale la pena ricordare che questo dispositivo è soggetto ad un piccolo difetto che potrebbe produrre comportamenti indesiderati e imprevedibili (sebbene molto poco probabili): per un breve periodo, dopo il fronte di salita del "clock" (10 ns, l'inevitabile ritardo di propagazione dell'inverter 74LS04), entrambi i sincronismi di memorizzazione E' e E" sono attivi contemporaneamente, cosicché entrambe le coppie di porte di controllo rimangono aperte.

Per questa ragione l'architettura didattica appena descritta è sostanzialmente ottimizzata nei componenti commerciali con l'aiuto dei Rivelatori di Transizione (o Rivelatori di Fronte d'onda, essi pure trattati nella precedente puntata), al fine di rendere attivi i due segnali di sincronismo E' e E" in tempi effettivamente separati e non sovrapposti; in questo modo Master e Slave risultano "trasparenti" per un tempo piccolissimo, in 2 posizioni ben distinte tra loro, dando grande affidabilità al dispositivo, da ritenersi ora un *Flip-Flop*, a tutti gli effetti.

Vediamo ora di analizzare la disponibilità commerciale di questi elementi di memoria; essa è veramente notevole: numerosi sono i componenti di tipo **D-Latch** (oggetto di questa e della prossima puntata) ma altrettanto importanti sono quelli di tipo **D-Type** (ora effettivamente Flip-flop), dotati del circuito Rivelatore di Transizione che trasforma il segnale di Abilitazione (ora effettivamente Clock) in un breve impulso, in corrispondenza di uno dei suoi fronti, detti Positive Edge Triggered, se si tratta di quello di salita, o Negative Edge Triggered SR, se si tratta di quello di discesa; ma questa è solo un'anticipazione che richiede un approfondimento da proporre più avanti, nel tempo.

## D-Latch (TTL): 74L875, 74L877, 74L8375

Tra quelli della serie **TTL** utilizzati con maggiore frequenza c'è il 74LS75, definito dai costruttori 4-bit Bistable Latches, utilizzato come memoria temporanea tra i microprocessori e le unità di input/output o di visualizzazione (come nel citato esempio dei BCD to 7-segment Latch/Decoder/Driver 4511 e 9368); quando la linea di abilitazione E è alta l'informazione presente sull'ingresso D è trasferita sull'uscita Q e continuerà ad essere copiata su di essa per

tutto il tempo che E rimane a 1; nell'istante in cui E passa a 0 l'informazione presente su D nel momento della transizione (fronte di discesa) viene agganciata in uscita e memorizzata fino a quando E tornerà a 1.

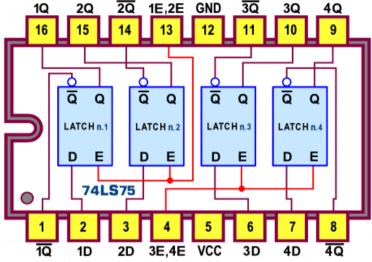

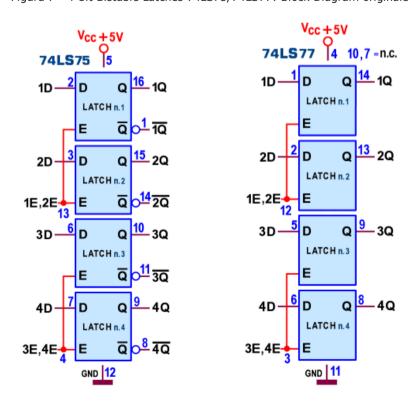

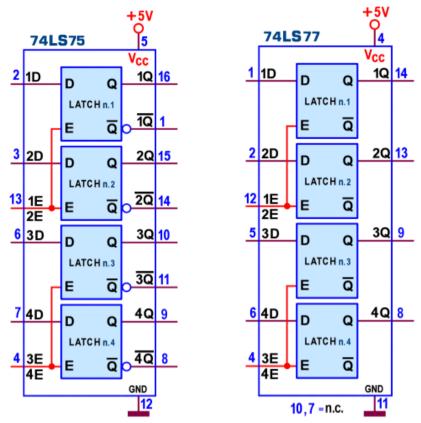

La Figura 5 mostra il suo pin-out, dal quale si nota che l'abilitazione è disponibile a coppie e che ciascun **D-Latch** rende disponibile sia l'uscita diretta Q che l'uscita negata Q.

Figura 5 - 4-bit Bistable Latches 74LS75: Pin-out

Curiosa anche la disposizione dei pin di alimentazione  $V_{CC}$  (pin 5) e GND (pin 12), posti entrambi in posizione centrale: si tratta di una caratteristica molto frequente nei componenti di prima generazione, probabilmente suggerita dal fatto di favorire il collegamento di un piccolo condensatore di disaccoppiamento direttamente a cavallo di entrambi; l'utilizzo di questi componenti (di solito di tipo ceramico a disco tra 10nF e i 100nF) è sempre fortemente consigliato nel progetto reale di dispositivi (sia digitali che analogici) per fugare a massa i disturbi in alta frequenza eventualmente sovrapposti al livello costante dell'alimentazione e per disaccoppiare (by-pass) le singole parti di un circuito, assicurando loro un buon funzionamento.

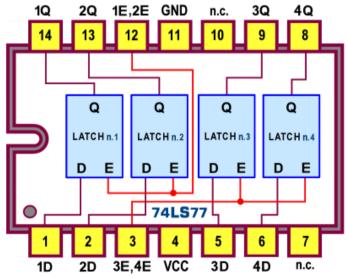

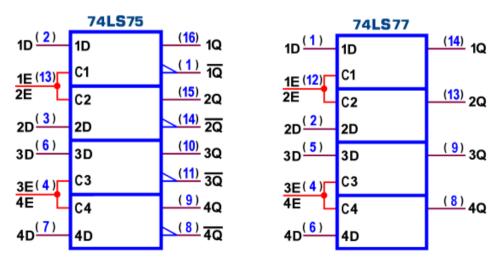

Figura 6 - 4-bit Bistable Latches 74LS77: Pin-out

Per ottenere l'effetto migliore è sempre opportuno porre il condensatore di by-pass direttamente a ridosso dei terminali di alimentazione dei circuiti integrati, per cui questa predisposizione sembra fatta apposta.

La Figura 6 mostra il pin-out del 74LS77, funzionalmente identico al precedente; si tratta sempre di un 4-bit Bistable Latches, organizzato ora in un contenitore a 14 pin, cosa che rende possibile ora la disponibilità delle sole uscite dirette Q.

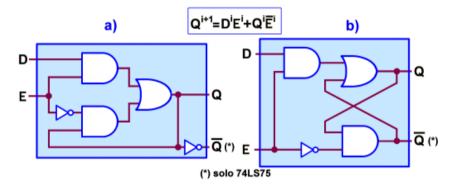

Per entrambi i manuali offrono lo schema logico (Block Diagram o Logic Diagram) di un singolo Latch: apparentemente esso può sembrare piuttosto ambiguo, per la scelta di coinvolgere tre operatori logici diversi; la Figura 7a mostra il circuito originale (ridisegnato nella classica forma retroazionata in Figura 7b) con il quale è facile dimostrare che la formula caratteristica è effettivamente la stessa di quella del circuito proposto in Figura 2; ricordo che la disponibilità dell'uscita negata Q vale solo per il 74LS75.

Figura 7 - 4-bit Bistable Latches 74LS75/74LS77: Block Diagram originale

Figura 8 - 4-bit Bistable Latches 74LS75/74LS77: Schema funzionale

Figura 9 - 4-bit Bistable Latches 74LS75/74LS77: Schema pratico

Lo schema funzionale complessivo per i 2 componenti è visibile in Figura 8, mentre lo schema pratico per entrambi è mostrato in Figura 9. In Figura 10 è disponibile per entrambi anche il simbolo logico predisposto dallo standard IEEE.

Figura 10 - 4-bit Bistable Latches 74LS75/74LS77: Simbolo logico ANSI/IEEE Std. 91-1984

La potenza massima dissipata dal 74LS75 è di 60 mW, di poco inferiore a quella dissipata dal 74LS77, pari a 65 mW; i ritardi di propagazione massimi (misurati con carico di 15pF) sono disponibili tra ingresso D e uscita diretta Q e tra ingresso E e uscita diretta Q (e tra i due ingressi e l'uscita negata Q, per il componente che ne dispone): mediamente oscillano tutti intorno ai **20 ns**, per entrambi i componenti e per entrambe le transizioni (**t**<sub>PLH</sub> e **t**<sub>PHL</sub>).

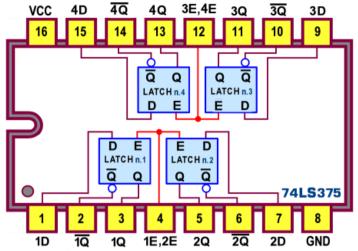

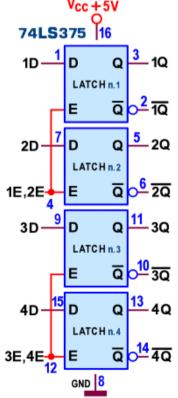

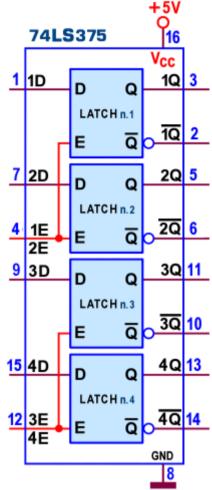

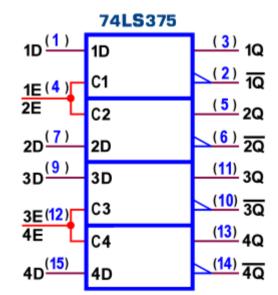

Il Latch bistabile 74LS375 è elettricamente e funzionalmente identico al 74LS75, diverso solo la disposizione dei terminali; per esso valgono le stesse informazioni appena descritte; la Figura 11 mostra il suo pin-out.

Figura 11 - 4-bit Bistable Latches 74LS375: Pin-out

Da notare che i pin di alimentazione V<sub>CC</sub> (pin 5) e GND (pin 12) sono ora nella classica posizione sugli angoli opposti del contenitore.

Lo schema funzionale (Figura 11BIS), lo schema pratico (Figura 11TER) e il simbolo logico dello standard IEEE (Figura 11QUATER) completano la documentazione di questo componente.

Figura 11BIS - 4-bit Bistable Latches 74LS375: Schema funzionale

Figura 11TER - 4-bit Bistable Latches 74LS375: Schema pratico non pubblicata]

Figura 11QUATER - 4-bit Bistable Latches 74LS375: Simbolo logico ANSI/IEEE Std. 91-1984 [non pubblicata]

## Registri D-Latch (TTL): 74100, 74LS373, 74LS573, 74LS533, 74LS563

I componenti descritti finora contengono elementi di memoria utilizzabili a coppie indipendenti tra loro, ma la necessità di interfacciare le logiche programmabili con uno strato di memoria temporanea (da offrire alle rispettive interfacce di input/output o di visualizzazione) suggerisce l'esigenza di utilizzare un numero maggiore di elementi singoli, di solito 4 o 8; questa struttura prende il nome di *Registro* ed è altamente diffusa, fino al punto di diventare importante parte strutturale delle stesse CPU.

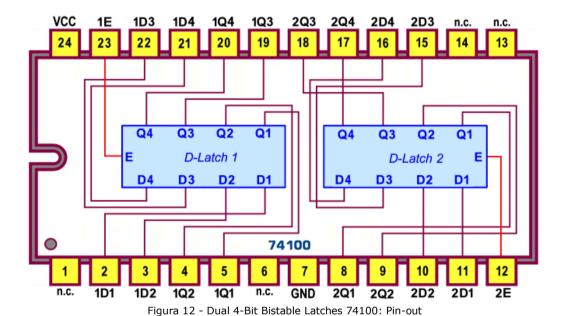

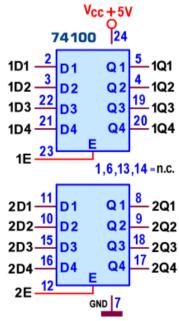

Un doppio **Registro D-Latch** a 4 bit (Dual 4-bit Bistable Latches) è disponibile nel 74100 della serie TTL standard; il funzionamento è lo stesso della coppia 74LS75/74LS77 vista in precedenza, dei quali costituisce in sostanza la versione doppia.

Figura 13 - Dual 4-Bit Bistable Latches 74100: Schema funzionale

Proponiamo il suo pin-out (Figura 12) e lo schema funzionale (Figura 13); con E=1 ciascun Latch è trasparente (l'informazione sugli ingressi D è trasferita continuamente sulle uscite Q) mentre il valore delle linee D presente in input quando si manifesta il fronte di discesa di E viene memorizzata, fino a quando E tornerà a 1.

Questo dispositivo può essere utilizzato come memoria temporanea a 4+4 o a 8 bit (collegando e attivando insieme le abilitazioni delle 2 metà).

Anche in questo caso è piuttosto curioso lo schema logico (Block Diagram o Logic Diagram, Figura 14a) offerto dai manuali per un singolo elemento di memoria: la versione ridisegnata (Figura 14b) lo rende compatibile con quella classica di Figura 2.

Figura 14 - Dual 4-Bit Bistable Latches 74100: Block Diagram originale

La potenza massima dissipata dal 74100 è di 530 mW (tipico TTL standard) mentre i ritardi di propagazione massimi (misurati con carico di 15pF/400ohm) tra ingressi D e uscite Q sono di **30** ns  $(t_{PLH})$  e **25** ns  $(t_{PHL})$ , sostanzialmente simili a quelli tra abilitazione E e uscite Q.

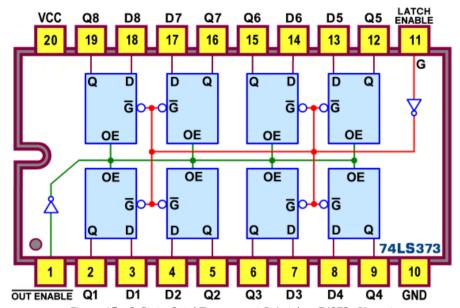

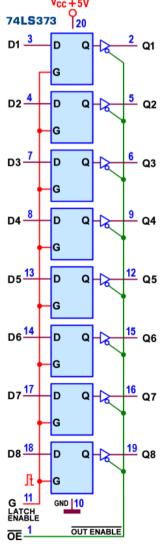

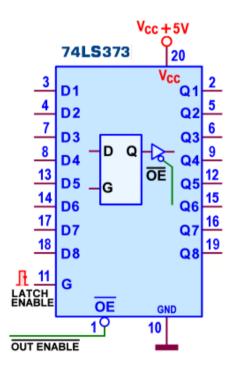

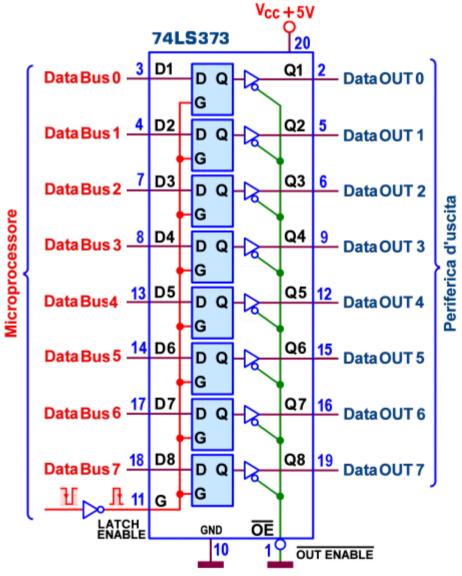

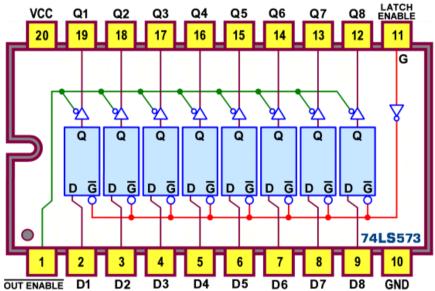

Il componente più importante di questa raccolta è certamente il 74LS373 (3-State Octal Transparent D-Latches) un Registro D-Latch in grado di gestire in blocco un'informazione di 8 bit, particolarmente utile nell'ambito dei microprocessori o dei single-chip per realizzare una porta d'uscita a cui affidare un byte d'informazione, per esempio per accendere 8 led, o pilotare 8 relè, o controllare i 7 segmenti (e il decimal point) di un digit, e così via; la Figura 15 mostra il suo pin-out.

Gli 8 **D-Latch** sono controllati contemporaneamente da un unico piedino di abilitazione G, che si comporta in modo assolutamente coerente con quanto già più volte detto: con G=1 ciascun Latch è trasparente (l'informazione sugli ingressi D è trasferita continuamente sulle uscite Q) mentre quando si manifesta il fronte di discesa di G viene memorizzato il valore presente in quel momento sulle linee D, e mantenuto fino a quando G tornerà a 1.

Oltre a garantire la sua tipica funzione di memoria questo componente offre anche uscite amplificate non invertenti di tipo 3-state, progettate specificamente per pilotare carichi con impedenza relativamente bassa e controllate contemporaneamente da un ulteriore piedino di abilitazione (Out Enable, OE), attivo basso, la funzione del quale è del tutto simile a quella esercitata dalle abilitazioni G del buffer 74LS244: quando è attiva (OE=0) consente il passaggio (sull'uscita effettiva) del livello logico presente sull'uscita interna del Latches, mentre quando non è attiva (OE=1) le 8 uscite esterne sono forzate in alta impedenza.

Figura 15 - 3-State Octal Transparent D-Latches 74373: Pin-out

Figura 16 - 3-State Octal Transparent D-Latches 74373: Schema funzionale

E' importante capire cosa significa mettere un'uscita in alta impedenza; supponiamo di applicare una tensione ad un resistore: la corrente che lo attraversa è soggetta alla legge di Ohm per cui, a parità di tensione applicata, più grande è la sua resistenza, minore è la corrente che passa; se la resistenza elettrica è infinita la corrente è nulla, cioè un resistore con questa caratteristica si comporta come un circuito aperto, come se esso stesso fosse sparito, lasciando scollegati i punti ai quali era collegato..

Dunque, la condizione di alta impedenza delle uscite scollega praticamente l'oggetto ad esse collegato, anche se fisicamente la cosa non si vede! Lo schema funzionale di Figura 16 mette in evidenza questa caratteristica; da notare che la linea di controllo OE non influisce sul funzionamento interno dei Latches cosicché i vecchi dati possono essere congelati sulle uscite interne (in attesa di tempi migliori ...) ed eventuali nuovi dati possono essere inseriti, anche mentre le uscite sono "scollegate".

La Figura 17 mostra lo schema pratico, consigliato nella stesura dei progetti per la sua sintetica completezza.

Figura 17 - 3-State Octal Transparent D-Latches 74373: Schema pratico

La possibilità di disporre dell'alta impedenza sulle uscite ci suggerisce di soffermare l'attenzione su un altro fatto: essa è utile nelle strutture organizzata a bus (tipiche del progetto con logiche programmabili): per esempio possiamo collegare più memorie 74LS373 in parallelo, attivandone all'occorrenza solo una, alternativa alle altre.

Di solito se si collegano tra loro le uscite di 2 oggetti logici si commette un errore fatale: si capisce che, se i livelli presenti sulle 2 uscite sono alternativi, una delle 2 (quella a livello 0) provoca il cortocircuito dell'altra, forzandola a massa con il suo 0...; ma se una delle 2 è posta in Hi-Z il problema non esiste più, dato che nessun livello logico può essere influenzato da un circuito aperto..

Di norma questa opzione non è necessaria, per cui OE si collega fisso a massa; la Figura 18 mostra lo schema di una tipica porta d'uscita (l'interfaccia tra le uscite di una CPU e gli ingressi di un utilizzatore); il fatto che l'impulso di sincronismo (solitamente generato dallo stesso processore) debba essere orientato verso un'abilitazione attiva sui livelli (tipica dei Latches) richiede alcune considerazioni: a) la memorizzazione del byte presente sul Bus Dati avviene sul fronte di discesa di G; b) per tutto il tempo in cui l'impulso su G rimane alto le uscite sono fortemente sensibili ad ogni variazione dei rispettivi ingressi, per cui è assolutamente indispensabile che esso sia breve e che i dati in ingresso siano stabili, almeno per un tempo un po' più grande della sua durata (cioè siano forniti poco prima e tolti poco dopo la sua presenza); c) per entrambe le precedenti ragioni, essendo gli impulsi di sincronismo (di norma) attivi bassi, per un corretto funzionamento del componente è necessario inserire un inverter direttamente sul pin 11 di Enable (G); d) la presenza dell'inverter esterno ritarda per altro l'effettiva memorizzazione di un tempo pari alla durata (di norma trascurabile) dell'impulso fornito, in aggiunta al suo tempo di propagazione (20 ns).

Figura 18 - 3-State Octal Transparent D-Latches 74373: Porta d'uscita

La potenza massima dissipata dal 74LS373 è di 200 mW; la corrente erogata tipica in uscita (con Q=1) e di 2,6 mA mentre quella assorbita tipica in uscita (con Q=0) è di ben 24 mA; i ritardi di propagazione massimi (misurati con carico di 45pF/667ohm) tra ingressi D e uscite Q sono di 18 ns per entrambe le transizioni ( $t_{PLH}$  e  $t_{PHL}$ ) e un po' più grandi (30 ns) tra abilitazione e uscite Q.

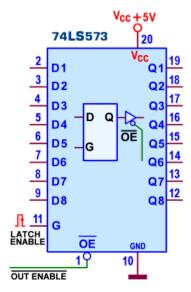

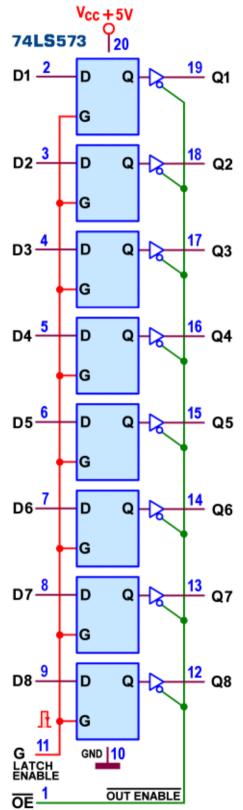

Osservando il componente precedente salta subito agli occhi la strana collocazione scelta dal costruttore per la disposizione degli ingressi D e delle uscite Q, posti a coppie dallo stesso lato del circuito integrato; questo fatto può aggiungere un disagio in più al progettista del circuito stampato chiamato ad ospitarli; probabilmente per questa ragione è stato reso disponibile il componente 74LS573, funzionalmente identico al precedente ma con tutti gli 8 ingressi sul lato sinistro del chip e tutte le 8 uscite sul lato destro.

La Figura 19 mostra il pin-out e la Figura 20 lo schema pratico.

Figura 19 - 3-State Octal Transparent D-Latches 74573: Pin-out

Figura 20 - 3-State Octal Transparent D-Latches 74573: Schema pratico

## In Figura 20BIS lo schema funzionale

Figura 20BIS - 3-State Octal Transparent D-Latches 74573: Schema funzionale [non pubblicata]

La potenza massima dissipata dal 74LS573 è di 250 mW; i ritardi di propagazione massimi (misurati con carico di 50pF/2kohm) tra ingressi D e uscite Q sono di 27 ns (tplh) e 18 ns  $(t_{PHL})$  e un po' più grandi tra abilitazione e uscite Q: 36 ns  $(t_{PLH})$  e 25 ns  $(t_{PHL})$ .

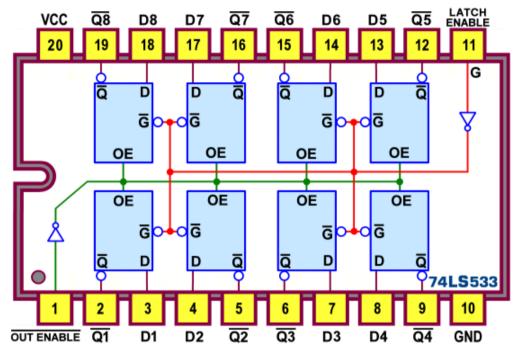

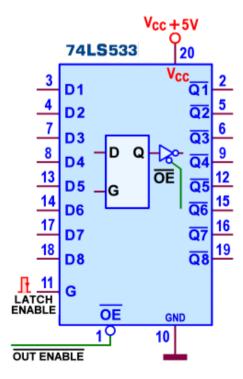

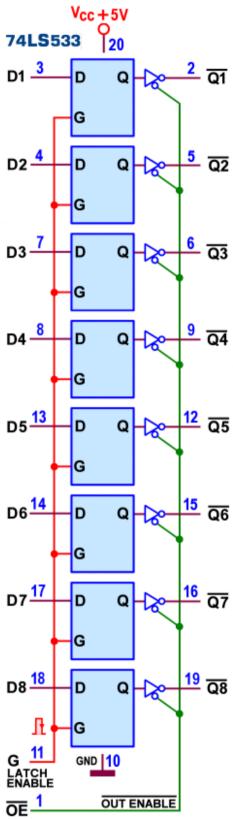

Del componente 74LS373 esiste anche una versione con uscite negate (3-state amplificate invertenti), ad esso funzionalmente identica, nota come 74LS533; la Figura 21 mostra il suo pin-out e la Figura 22 il relativo schema pratico.

Figura 21 - 3-State Octal Transparent D-Latches 74533: Pin-out

Figura 22 - 3-State Octal Transparent D-Latches 74533: Schema pratico

In *Figura* 22BIS lo *schema* funzionale.

Figura 22BIS - 3-State Octal Transparent D-Latches 74533: Schema funzionale [non pubblicata]

La potenza massima dissipata dal 74LS533 è di 230 mW; i ritardi di propagazione massimi (misurati con carico di 50pF/2kohm) tra ingressi D e uscite Q sono di 23 ns per entrambe le transizioni (t<sub>PLH</sub> e t<sub>PHL</sub>) e un po' più grandi (30 ns) tra abilitazione e uscite Q.

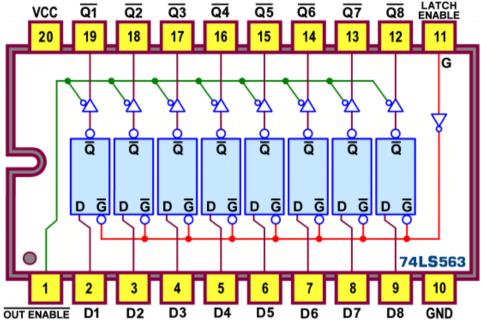

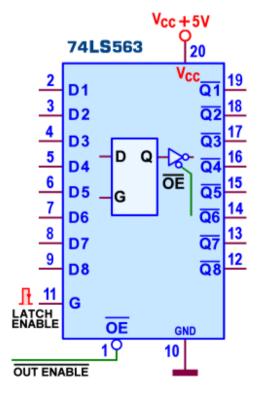

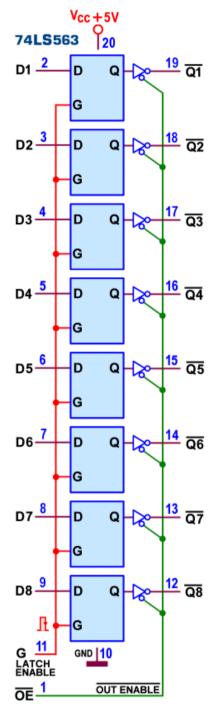

Anche per questo componente con uscite negate esiste una versione funzionalmente identica ma con tutti gli 8 ingressi sul lato sinistro del chip e tutte le 8 uscite sul lato destro; si tratta del 74LS563, del quale la Figura 23 mostra il pin-out e la Figura 24 offre lo schema pratico.

Figura 23 - 3-State Octal Transparent D-Latches 74563: Pin-out

Figura 24 - 3-State Octal Transparent D-Latches 74563: Schema pratico

In Figura 23BIS lo schema funzionale.

Figura 23BIS - 3-State Octal Transparent D-Latches 74563: Schema funzionale

La potenza massima dissipata dal 74LS563 è di 200 mW; i ritardi di propagazione massimi (misurati con carico di 50pF/2kohm) tra ingressi D e uscite Q sono di 23 ns per entrambe le transizioni (t<sub>PLH</sub> e t<sub>PHL</sub>) e un po' più grandi (35 ns) tra abilitazione e uscite Q.

Questa trattazione continuerà la prossima puntata con due curiose categorie di D-Latch (gli Addressable Latch e i Cascadable Priority Register) e con la descrizione dei componenti della serie CMOS.